06_pixel_assembly.md 16 KB

title: Phase I Silicon Detector Assembly ...

Overview

The CMS Phase I Upgrade project was an effort to design and construct an improved detector for Run II of the LHC.

Automated Assembly

Gantry Software

Quality Control

Results

The Phase II telescope

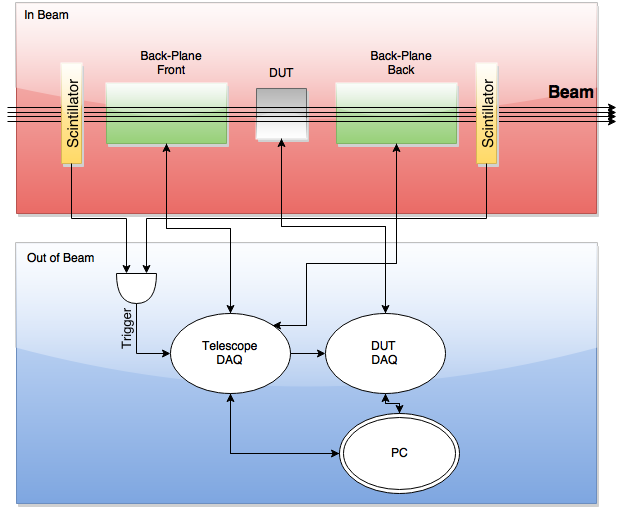

In anticipation of test beams to commission detector elements of the Phase II Upgrade of the CMS detector, a telescope was designed to serve as a reference measurement. The design of the telescope is centered around several layers of silicon strip sensors placed fore and aft of the device under test (DUT). Hits in the strips are correlated to construct a track. This track is then projected onto the DUT, yielding residuals that can be used to characterize the DUT.

[@Fig:telescope_hierarchy] shows a block diagram of the telescope in operation.

Design

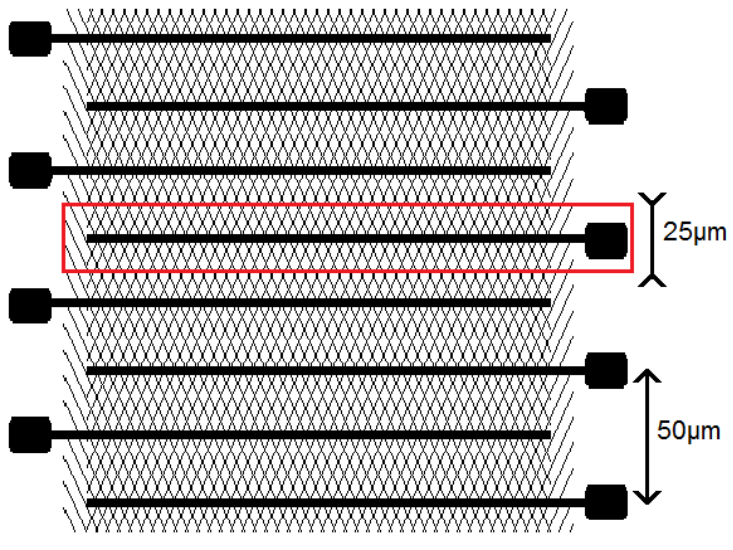

The telescope's several layers of sensing material consist of silicon micro-strip sensors. These particular sensors consist of 512 strips of 25 $\mu$m pitch. The metalization that defines the strips has readout pads on alternating sides of the chip leading to 50 $\mu$m pitch on the pads along either side. [@Fig:telescope_sensor] illustrates this pattern.

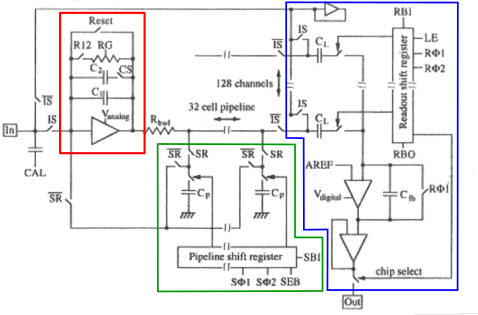

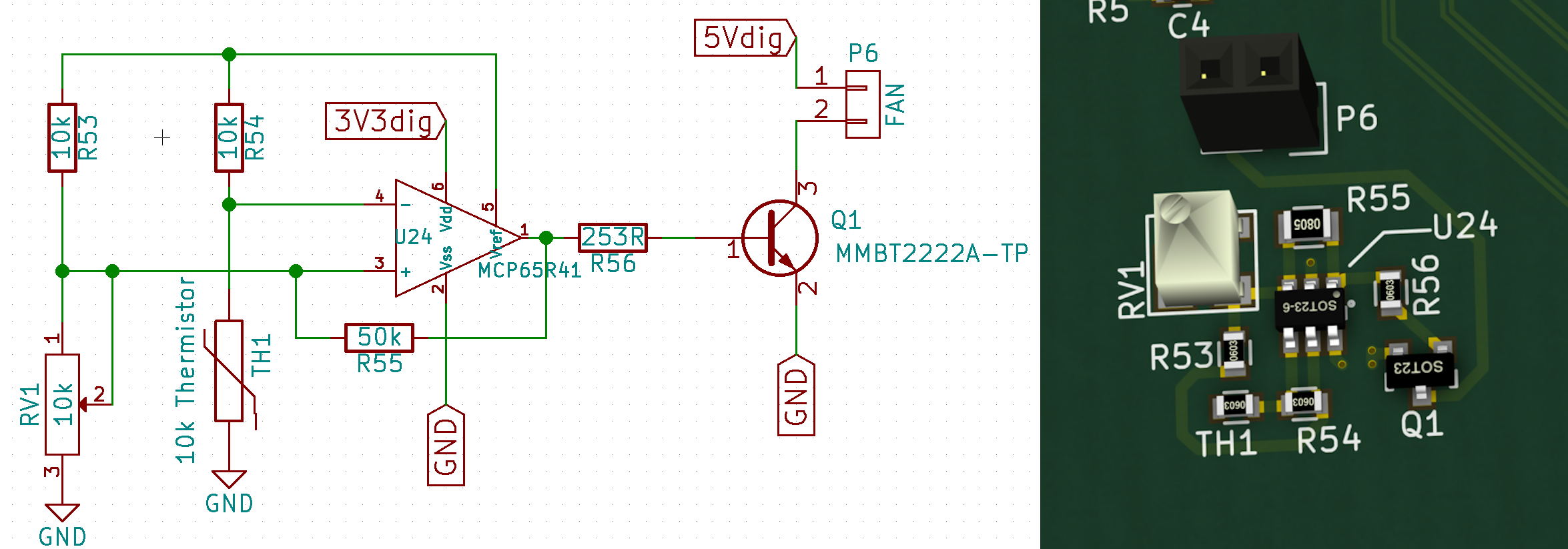

The sensor is read out with an integrated circuit called the Analog Pipeline Chip - 128 (APC128). Each APC128 is has a 128 channels which correspond to reading out 128 strips of a silicon micro-strip sensor. [@Fig:apc128] shows an operational schematic detailing one of these channels. Going from left to right, the circuit consists of a pre-amplifier, the sampling capacitors, and readout pipeline. Lets look at each of these in turn.

When the APC128 is in sampling mode $SR$ is high, meaning that the switches labeled $SR$ are closed and the switches labeled $\bar{SR}$ are open, and $IS$ is high. Lets also assume that $Reset$, $R12$, and $CS$ are low for now. In this configuration any current originating from $In$ flows onto $C_1$. The pre-amplifier will sink the charge that was removed from the right "plate" of $C_1$ to keep it electrically neutral. In the end, the preamplifier now has a voltage to maintain on its output that is proportional to the charge read from the sensor. If the $R12$ signal goes high, some of the charge from $C_1$ is allowed to bleed off over time so the voltage of the pre-amplifier will spike with input current and slowly return to its original value. $R12$ also keeps leakage current from saturating the pre-amplifier. On the other hand, if $Reset$ goes high, all of the charge is quickly removed and the pre-amplifier immediately returns to its original state. In a testing environment with bunched particles, the $Reset$ signal may be timed with the beam crossing to clear out the channel between bunches. However, if there is ambiguity when particles could potentially arrive, it is useful to keep a series of periodic samples of the input signal and then read out the correct one when a trigger is received.

Each channel has 32 sampling capacitors, labeled $C_p$ in the schematic. A bit is shifted through the "Pipeline shift register" which connects the output of the pre-amplifier to one $C_p$ at a time. When the pre-amplifier is connected to a particular $C_p$, that capacitor gets charged to a voltage proportional to the input signal at that time. As the bit moves through the shift register, it takes a series of 32 samples of the input signal. Having a time series of samples is important because there is generally a time delay between when the signal from the sensor arrives and when a trigger makes its way through the trigger system to the chip. Without a history of samples, the pulse height information will be lost by the time a trigger arrives.

When a trigger arrives, sampling of the input stops. A specific $C_p$ is selected with the pipeline shift register based on a pre-calibrated trigger delay, and the $SR$ and $IS$ signals go low. This hooks up the $C_p$ capacitor back to the input of the preamplifier. A bit is shifted into the "Readout shift register" which connects each of the 128 channels sequentially to the output stage. When a particular channel is connected to the output stage, The preamplifier charges the $C_L$ capacitor which in turn places a voltage across $C_fb$ and causes the output amplifier to supply an analog voltage that is proportional to the magnitude of the original pulse from the silicon micro-strip sensor. As the bit in the readout shift register works its way through the channels, a series of analog voltages are supplied to the output which ultimately represent the charge deposits on each of the 128 strips the particular chip is connected to.

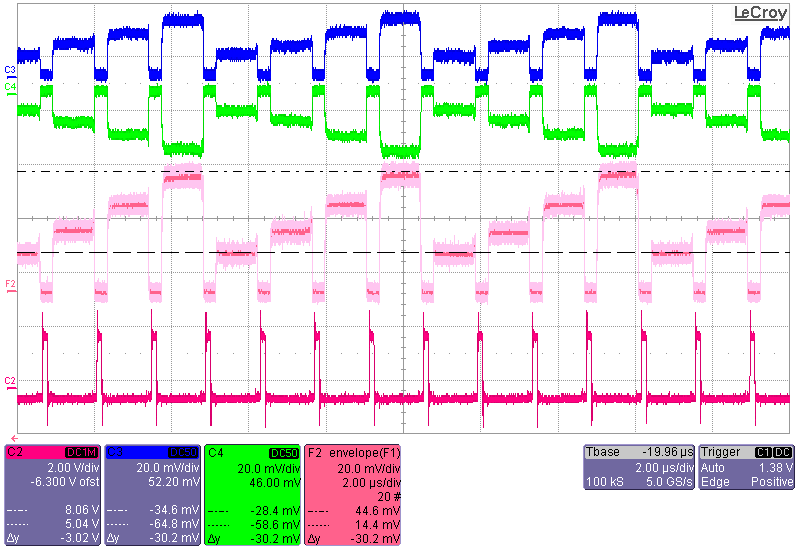

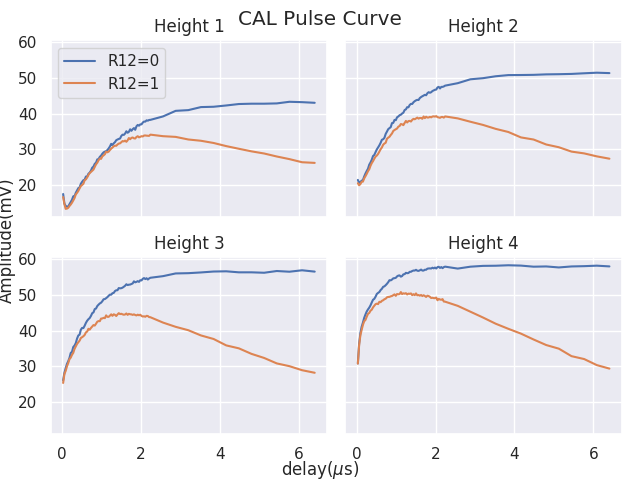

For calibration and testing, the input of the preamplifier is given a charge through the $CAL$ input. There is a separate $CAL$ capacitor for each channel with values that cycle starting with C, then 2C, 3C, 4C, and back to C. The different capacitor values give different charge inputs to the pre-amplifiers for a shared calibration voltage. As the different channels are readout, the analog output voltage will step through four discrete values corresponding to the four different capacitor values. [@Fig:step_curve] shows what this "step curve" looks like.

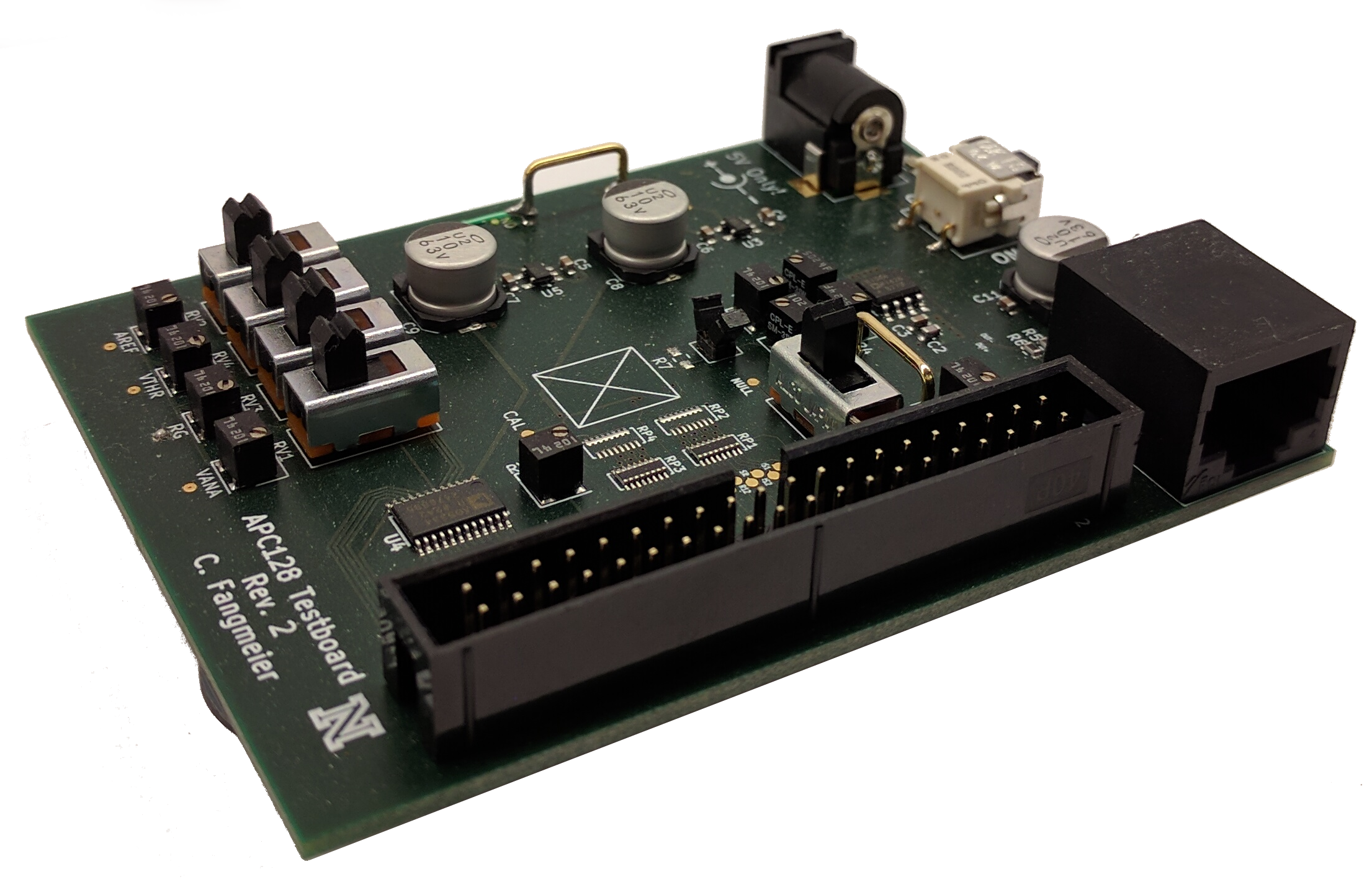

The APC128 was originally developed for the HERA experiment at DESY[@Hilgers2001] in the 1990s. In the decades since, Much expertise on the operation and performance of the chip has been lost, and very little technical documentation is available. Therefore, in order to better understand the operation of the chip a dedicated testboard was designed as part of the telescope R&D. [@Fig:step_curve] was acquired with the aide of this test board, an image of which is shown in [@fig:apc128_testboard].

Developing the signal patterns that correctly operate the chip to produce the step curve was a significant achievement. This is simply because even a small error in the pattern can result in erroneous output, with little indication of exactly which signal was wrong and at which clock cycle. To aide in the development of the control signal patterns, software was developed to convert a simple text-based representation of the pattern to FPGA firmware that would actually generate those patterns. [@Fig:apc_pattern] shows an excerpt from one of these patterns. A - indicates that the digital signal is high during a clock cycle while a _ indicates it is low. This excerpt shows the pipeline selection bit being shifted through the pipeline shift register of the APC128 while at some point the CAL signal goes from high to low, injecting some charge into the preamplifier. The preamplifier will then charge up the currently selected pipeline capacitor. A following section of the pattern will select this capacitor for readout and shift through all 128 channels, producing the step curve.

Studies were also done to observe the shape of the pulse when charge is injected into the pre-amplifier via the calibration capacitor. This is shown in [@fig:pulse_decay]. The plot clearly shows the increasing magnitude of the output signal with increasing calibration capacitance, as well as the decay of the signal when the feedback resistor is enabled.

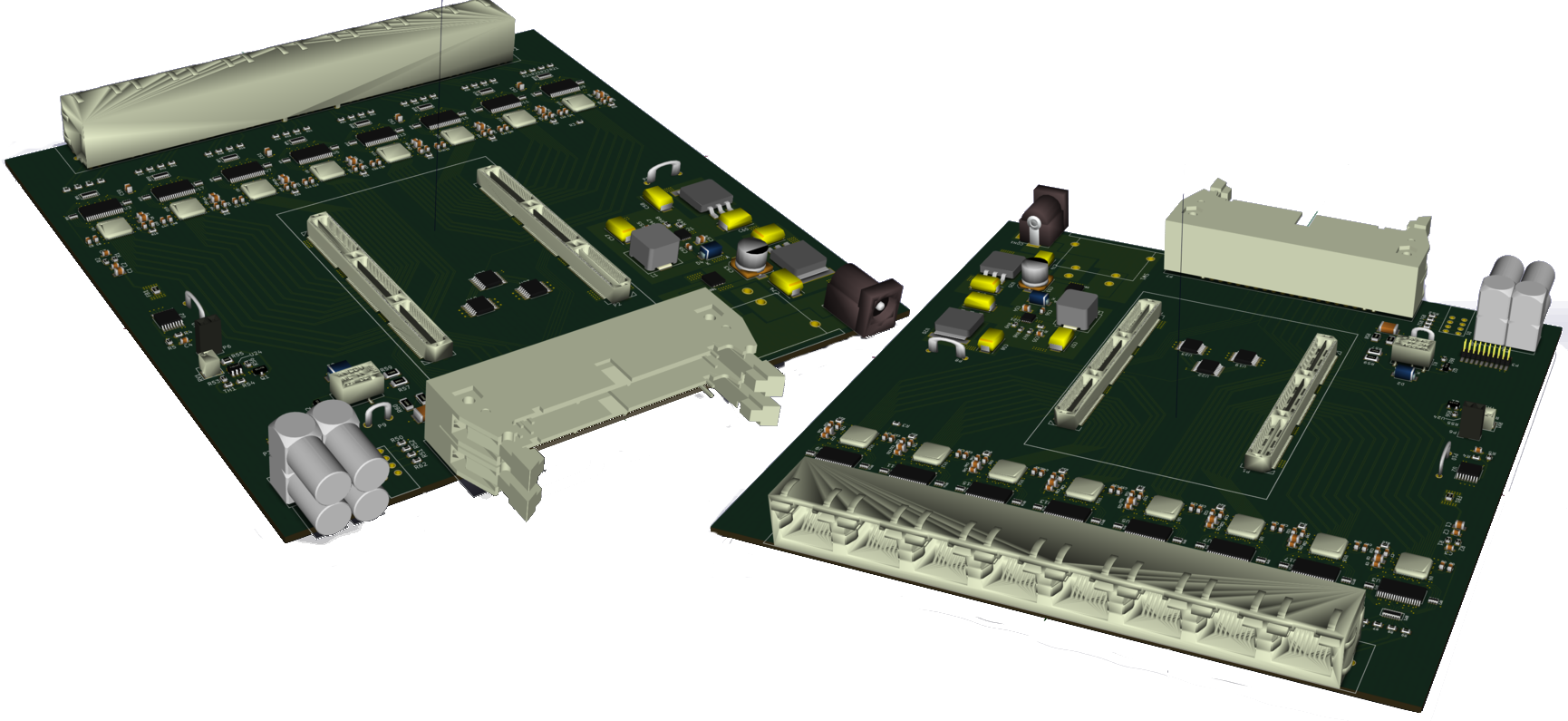

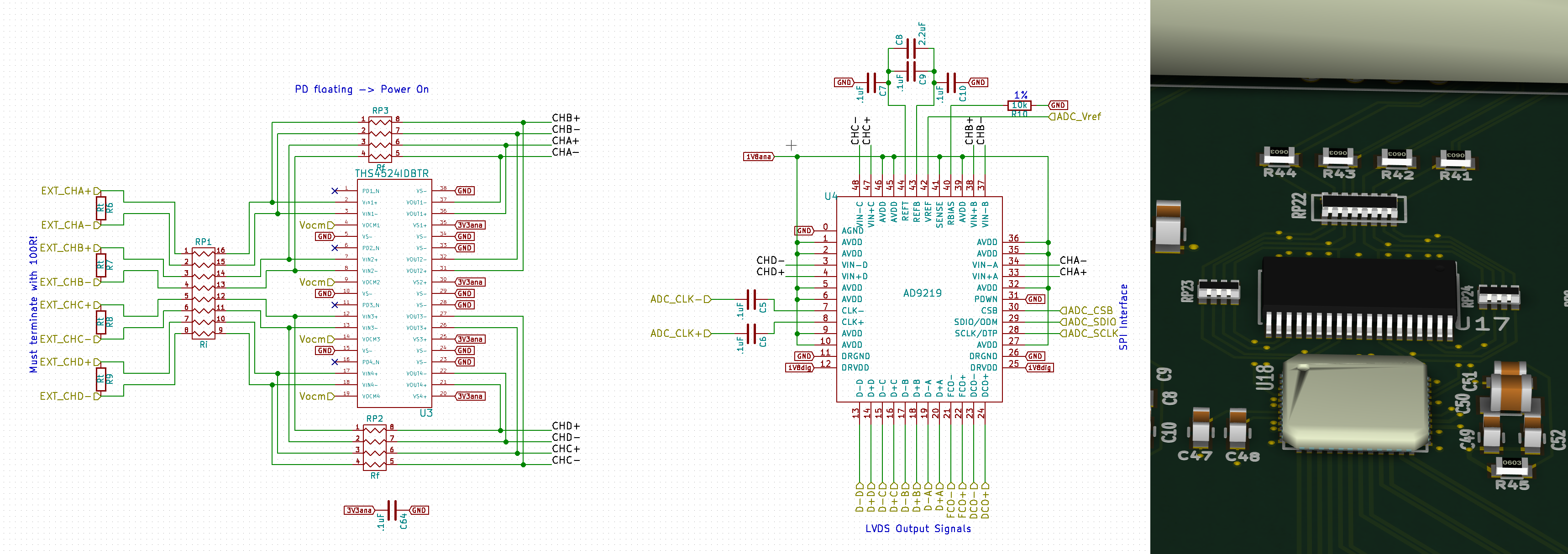

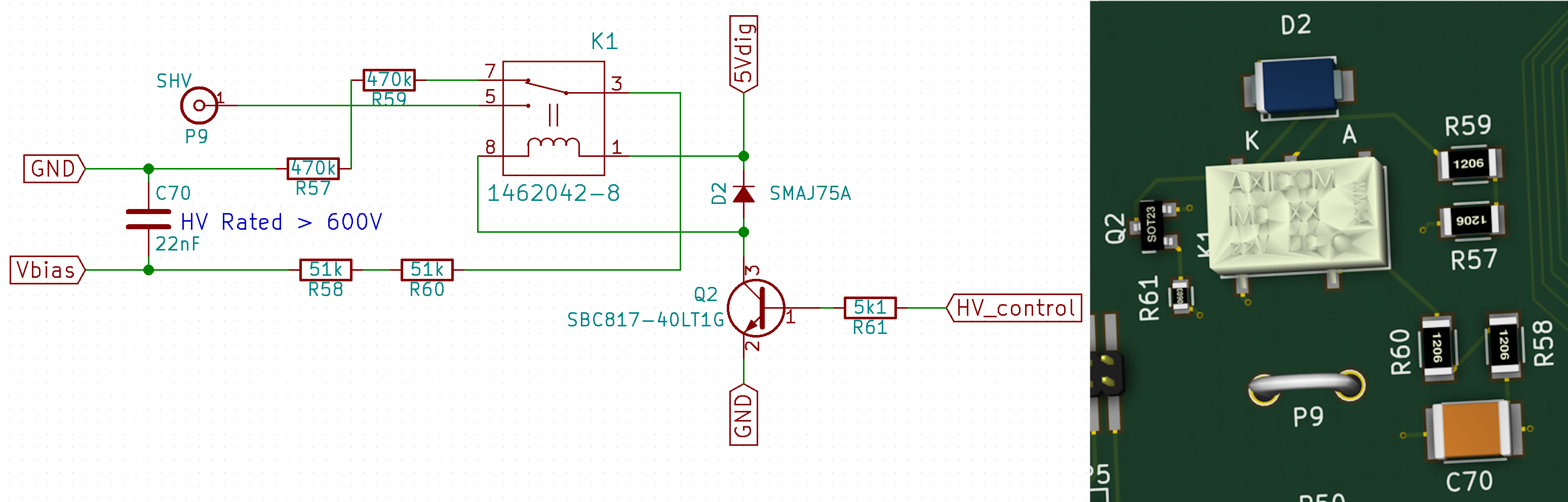

The design of the telescope calls for four layers of detector on each side of the DUT. Each layer will contain one silicon micro-strip detector with four APC128 chips to read out all 512 strips. The analog output of the APC128 has relatively high impedance[@Ryser2013] which implies the need for a nearby amplifier to drive the signal through the connections that lead out of the beam area to the DAQ. This may be a distance of up to several meters, depending upon the beam site. Based on these requirements, the AD8138ARZ differential amplifier was chosen to drive the signal and twisted pairs in a CAT-5 (ie Ethernet) cable were chosen to carry the signal. The board that carries the micro-strip detector, APC128, and amplifiers is referred to as a sensor card. There are four sensor cards mounted onto each of two identical back-plane boards as shown in [@fig:back_plane_board].

The back-plane board would be physically mounted to supports to bold the sensors in the beam path. It has four RJ-45 ports for the CAT-5 cables that route the differential analog signals to the DAQ and a 2x20 parallel connector for the DAQ to supply the APC128 control signals, bias voltage, and other miscellaneous signals required by the sensor cards.

The DAQ has four main jobs:

- Generate the control patterns for the APC128. This includes the pattern to continuously sample the pre-amplifier and the pattern to select the correct sample from each channel and readout the samples.

- Digitize the analog signals coming from the 32 APC128 chips. To minimize downtime during readout, all 32 are digitized in parallel.

- Pre-process the readings to suppress noise and identify hits.

- Transmit the collected hit data to a connected PC for further processing and storage.

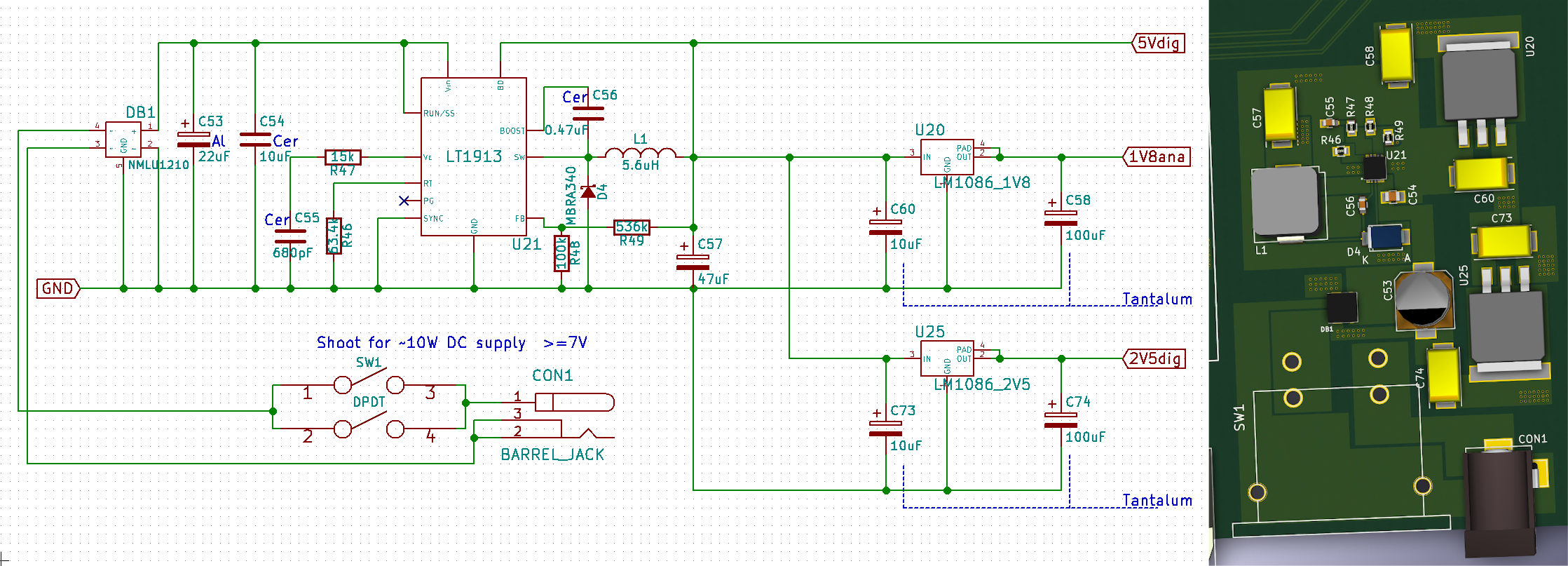

To accomplish these goals, a DAQ board, shown in [@fig:daq_overview], was designed and built. Not shown in the figure is the brains of the board: an Opal Kelly ZEM4310 FPGA integration board. The ZEM4310 plugs into the two central HSMC connectors which connect the FPGA to power, the ADCs, the APC128 control pattern lines, and other utility circuits. The ZEM4310 was chosen for its high amount of I/O, USB3 connectivity, and, importantly, its use of an Altera FPGA, a part that the DAQ designer already had experience programming.

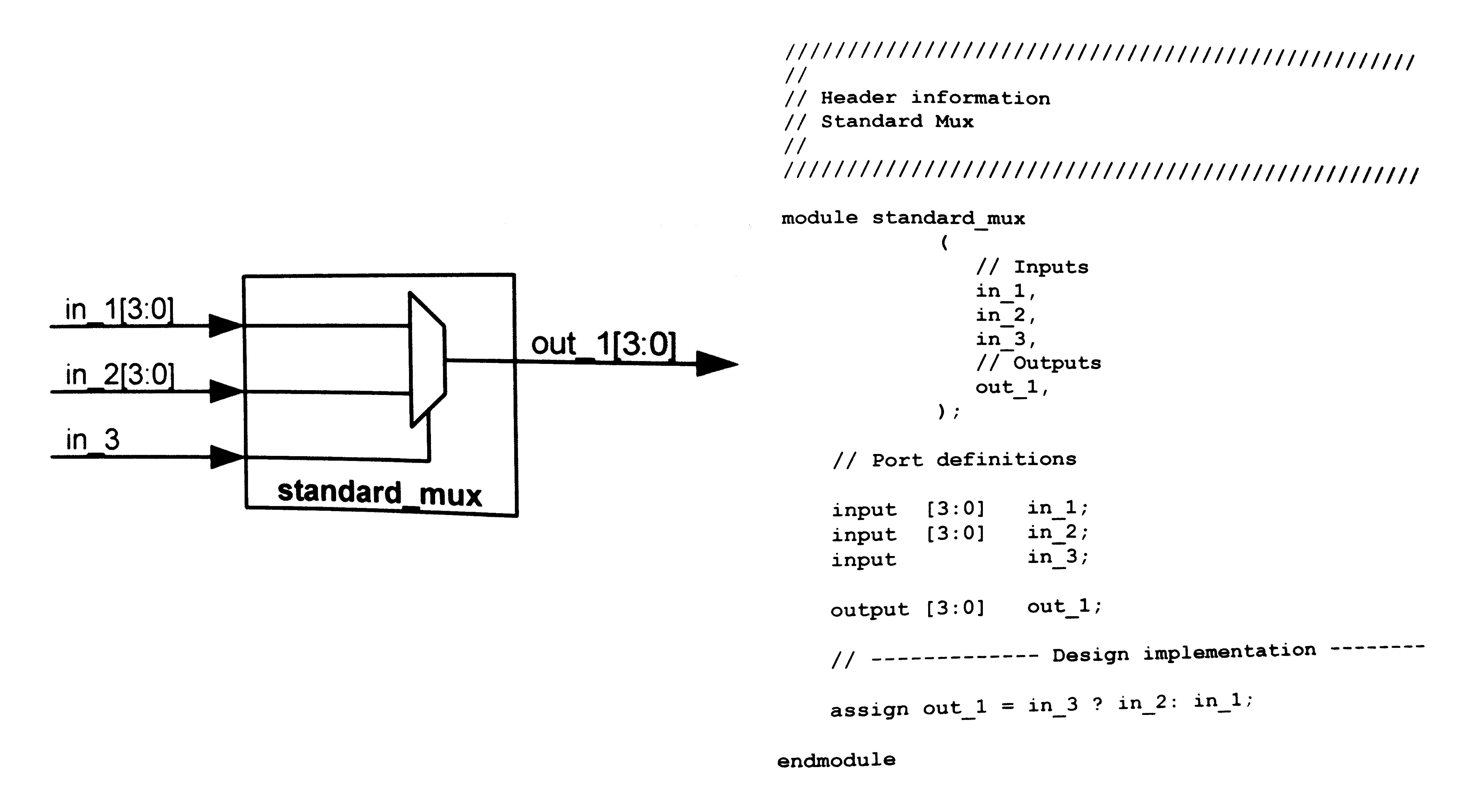

An FPGA is a dynamic and programmable piece of hardware. Unlike micro-controllers, however, an FPGA is able to directly emulate bare-metal logic circuits. This means that specialized digital circuits can be designed to handle specific tasks quickly, efficiently, and parallelized when necessary. The downside of this, however, is that FPGAs are not programmed with a typical programming language like C++ or Python, but instead use a special hardware design language. There are two popular language choices for FPGA design: Verilog, and VHDL. There is also a "block diagram" visual style of programming that some IDEs support. For the DAQ software, Verilog was chosen due to its more "C-like" syntax over the more verbose VHDL. [@Fig:verilog_sample] shows a sample of some Verilog code.

Talk about DAQ Firmware and Software